数字集成电路版图设计基础 Cadence IC 原理图绘制与仿真研发实践

数字集成电路版图设计是现代半导体工业的核心环节之一,它将逻辑设计转化为物理实现,直接决定了芯片的性能、功耗、面积与可靠性。在这一复杂流程中,使用专业电子设计自动化工具进行前端原理图设计、仿真与验证,是确保设计正确性与高效性的基石。本文将围绕Cadence IC设计平台,系统阐述数字集成电路原理图绘制与仿真研发的关键步骤与最佳实践。

一、 Cadence IC 设计平台概述

Cadence Integrated Circuit (IC) 设计平台是全球领先的EDA解决方案,为数字、模拟及混合信号集成电路设计提供了一整套完整、集成的工具链。对于数字集成电路前端设计,其核心组件通常包括:

- Virtuoso Schematic Editor: 强大的原理图编辑器,用于创建和编辑晶体管级或门级的电路原理图。它支持层次化设计,便于管理复杂模块。

- Analog Design Environment (ADE) / ADE Explorer/L: 集成的仿真环境,用于配置仿真参数、运行仿真并分析结果。它与多种仿真引擎无缝集成。

- Spectre / Spectre X / UltraSim 等仿真器: 高性能、高精度的电路仿真引擎,用于执行直流、交流、瞬态、噪声等多种分析,验证电路的功能和性能。

二、 原理图绘制:从概念到电路图

原理图是电路的图形化表示,是设计者与EDA工具沟通的桥梁。在Cadence Virtuoso中进行原理图绘制,通常遵循以下流程:

- 库与单元管理: 需要建立或加载包含标准单元、I/O单元、定制晶体管等基础元件的工艺设计套件库。所有设计都创建在特定的设计库中。

- 创建电路单元(Cell): 新建一个“Cellview”,类型选择“Schematic”。这是设计的基本单元。

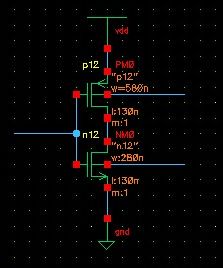

- 放置与连接器件: 从元件库中调用所需器件(如NAND、NOR、DFF等标准逻辑门或晶体管),放置在绘图区域。使用导线工具根据逻辑功能连接各器件的端口,构成完整电路。对于复杂设计,可以采用层次化方法,将子电路封装成符号(Symbol),在顶层原理图中作为模块调用。

- 添加端口与属性: 为电路定义输入、输出及电源/地端口。为关键器件或网络添加必要的属性,如晶体管尺寸(Width/Length)、负载电容等,这些参数直接影响仿真结果。

- 电气规则检查: 利用工具内置的检查功能,确保原理图中没有电气连接错误,如短路、开路、悬浮节点等。

三、 仿真研发:验证与优化设计

原理图绘制完成后,必须通过仿真来验证其功能正确性和性能指标。这是研发过程中迭代和优化的关键步骤。

- 仿真环境设置: 在ADE中打开对应的原理图Cellview。主要配置包括:

- 选择仿真器: 根据需求选择Spectre(高精度)或UltraSim(大容量快速仿真)等。

- 设置分析类型:

- 瞬态分析: 验证电路在时域下的动态行为,如逻辑功能、时序(建立/保持时间、传播延迟)、功耗波形等。需设置仿真时间、步长等。

- 直流分析: 分析电路的直流工作点、传输特性、噪声容限等。

- 蒙特卡洛分析/工艺角分析: 评估工艺偏差、温度电压变化对电路性能的影响,确保设计的鲁棒性。

- 定义激励信号: 为输入端口添加电压源或电流源,模拟真实的输入信号(如时钟、脉冲、数据序列)。

- 设置输出变量: 指定需要观察的信号节点电压、支路电流或计算得到的性能参数(如延迟、功耗)。

- 运行仿真与调试: 启动仿真后,工具会进行计算。如果仿真报错或结果异常,需要返回原理图或仿真设置进行检查和调试。常见问题包括收敛失败、激励设置不当、器件模型问题等。

- 结果分析与报告: 仿真完成后,利用ADE Results或Waveform Viewer查看波形、测量参数。例如,在瞬态波形中测量关键路径的延迟,计算平均动态功耗,检查逻辑电平是否正确。可以将测量结果保存并生成报告,作为设计达标与否的依据。

- 设计迭代与优化: 根据仿真结果,如果性能不满足规格(如速度太慢、功耗过高),则需要返回修改原理图。可能的优化措施包括:调整晶体管尺寸、改变电路拓扑结构、优化驱动强度、插入缓冲器等。然后再次仿真,直至所有指标达标。

四、 研发实践要点与挑战

在真实的研发项目中,数字集成电路原理图仿真还需关注:

- 模型准确性: 仿真结果严重依赖于器件模型文件(.lib, .scs)。必须使用由晶圆厂提供的、经过硅验证的精确模型。

- 仿真精度与效率的权衡: 对于全定制高性能模块(如SRAM、锁相环),需要高精度仿真;对于大规模数字逻辑,可能采用更快的仿真器或抽象模型以提高效率。

- 与后续流程的衔接: 前端原理图仿真验证的功能和时序,需要与后续的版图设计、寄生参数提取及后仿真结果进行一致性比对,确保物理实现不引入额外问题。

- 团队协作与版本管理: 在大型项目中,原理图和仿真测试平台需要纳入版本控制系统进行管理,确保团队成员工作同步。

###

熟练掌握Cadence IC平台进行原理图绘制与仿真,是数字集成电路研发工程师不可或缺的核心技能。它不仅是将设计思想转化为可靠电路的必要手段,更是通过反复迭代、验证与优化,最终实现高性能、低功耗芯片目标的关键保障。随着工艺节点的不断演进,仿真工具的智能化和模型的重要性将日益凸显,要求设计者不仅精通工具操作,更需深入理解电路物理本质与工艺特性。

如若转载,请注明出处:http://www.laike-cloud.com/product/43.html

更新时间:2026-01-13 15:35:13