集成电路CAD课程实验报告 二输入与非门电路设计与版图仿真

一、 实验目的

本实验旨在通过使用集成电路计算机辅助设计工具,完成一个标准CMOS二输入与非门(NAND2)的全流程设计,包括电路图设计、逻辑功能验证、版图设计与物理验证,以及后仿真分析。通过本实验,深入理解CMOS数字集成电路的基本单元结构、设计方法、版图设计规则以及从电路到版图的实现过程。

二、 实验内容

- 电路设计与前仿真: 在电路图编辑环境中,搭建CMOS二输入与非门电路,进行直流分析、瞬态分析,验证其逻辑功能(00→1, 01→1, 10→1, 11→0)和关键电学特性(如传输延迟、功耗)。

- 版图设计: 根据给定的设计规则(DRC),在版图编辑器中绘制二输入与非门的物理版图。版图需包含两个串联的PMOS管和两个并联的NMOS管,以及VDD、GND、输入A/B和输出Y的金属连接。

- 物理验证: 对完成的版图进行设计规则检查(DRC)和电路与版图一致性检查(LVS),确保版图符合工艺要求且与原始电路图在电学上等效。

- 寄生参数提取与后仿真: 从验证通过的版图中提取寄生电阻和电容(RC提取),生成包含寄生效应的仿真网表,并进行后仿真。对比前仿与后仿结果,分析寄生效应(如连线延迟)对电路性能的影响。

三、 实验原理

CMOS二输入与非门的布尔表达式为:Y = /(A·B)。其电路结构由两部分组成:

- 上拉网络(PUN): 由两个PMOS管并联构成。当A和B均为高电平时,两个PMOS管均关闭;其他任何输入组合下,至少有一个PMOS管导通,将输出Y上拉至VDD(逻辑1)。

- 下拉网络(PDN): 由两个NMOS管串联构成。仅当A和B均为高电平时,两个NMOS管同时导通,将输出Y下拉至GND(逻辑0)。

版图设计是将这种晶体管级的电路连接关系,转化为符合特定集成电路制造工艺几何规则和电学规则的物理掩模图形。设计时需遵循最小线宽、最小间距、阱和衬底接触等规则,并考虑器件匹配、连线优化以减少寄生效应。

四、 实验步骤与结果分析

- 电路图设计与前仿真:

- 使用Cadence Virtuoso Schematic Editor搭建电路。PMOS和NMOS的宽长比(W/L)根据驱动能力和速度要求进行初步设定(例如,PMOS W/L设置为NMOS的2-2.5倍以补偿空穴迁移率较低的问题)。

- 使用Spectre仿真器进行瞬态分析。输入A、B施加包含所有四种组合的脉冲信号。仿真波形清晰显示输出Y完全符合与非逻辑功能。测量得到(在典型工艺角下)输出由高到低的传输延迟(tphl)和由低到高的传输延迟(tplh),并估算平均静态功耗和动态功耗。

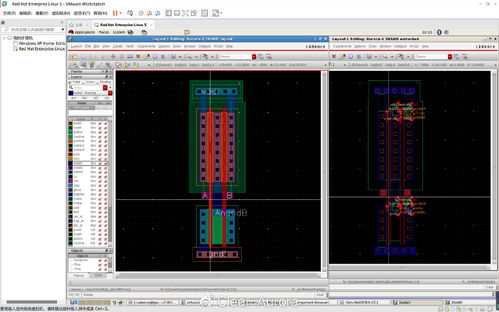

- 版图设计与物理验证:

- 使用Virtuoso Layout Editor绘制版图。关键步骤包括:

- 绘制N-well,并在其中布置两个并联的PMOS管,共享源极(接VDD)和N-well接触。

- 在P-substrate上布置两个串联的NMOS管,共享源极(接GND)和衬底接触。

- 使用Poly硅栅连接两个输入信号A和B,确保PMOS和NMOS的栅极正确对齐。

- 使用Metal1完成晶体管源/漏极的内部连接以及到电源、地和输出节点的连接。

- 添加输入/输出端口(PIN)。

- 运行DRC检查,根据报错信息修改版图,直至无任何违反设计规则的错误。

- 运行LVS检查,提供网表对比。成功通过LVS,证明版图与原理图在晶体管类型、数量及连接关系上完全一致。

- 寄生参数提取与后仿真:

- 对通过验证的版图进行RC提取(使用Quantus或类似工具),生成包含所有寄生电阻和电容的详细网表(SPICE格式)。

- 使用该网表进行后仿真,施加与前仿真相同的测试向量。

- 结果对比分析: 后仿真波形显示逻辑功能依然正确,但信号的边沿变得略微平缓,传输延迟明显增加。例如,tphl和tplh可能比前仿结果增大20%-50%,具体数值取决于工艺节点和版图布线长度。这是由于金属连线和通孔的寄生电阻电容引入了额外的RC延迟。动态功耗也可能因对寄生电容充放电而略有上升。此结果凸显了在深亚微米设计中,互连线延迟已成为制约电路性能的关键因素,版图优化(如缩短关键路径连线、使用高层金属等)至关重要。

五、 实验结论与研发意义

本次实验成功完成了CMOS二输入与非门从电路设计到物理实现的完整流程。通过前仿真验证了逻辑功能的正确性,通过版图设计实现了电路的物理描述,并通过DRC/LVS确保了其可制造性和电学等效性。通过后仿真定量分析了寄生参数对电路性能(主要是速度)的影响。

从研发角度而言,本实验所练习的全流程是现代数字集成电路芯片研发中标准单元库开发、定制电路模块设计的基础环节。掌握这一流程意味着:

- 理解了电路性能(速度、功耗、面积)与晶体管尺寸、版图布局之间的内在联系,为后续电路优化提供了依据。

- 熟悉了使用EDA工具进行自动化验证(DRC/LVS)和寄生提取的方法,这是保证芯片设计一次成功(First Silicon Success)的关键质量保障步骤。

- 认识到前端电路设计与后端物理实现必须协同考虑(设计协同),尤其是在高性能或低功耗设计中,需要迭代优化以达到设计目标。

因此,本实验不仅是学习工具使用的实践课,更是通向实际集成电路研发工作的重要桥梁。

如若转载,请注明出处:http://www.laike-cloud.com/product/41.html

更新时间:2026-01-13 20:24:23