CMOS集成电路设计中的逻辑门电路分析

在当今的数字电子世界中,互补金属氧化物半导体(CMOS)技术是超大规模集成电路(VLSI)的基石。其核心构件——CMOS逻辑门电路,以其低功耗、高噪声容限和优异的可扩展性,主导着从微处理器到存储芯片的几乎所有数字系统设计。深入分析CMOS逻辑门的工作原理、特性及设计考量,是掌握集成电路设计的关键。

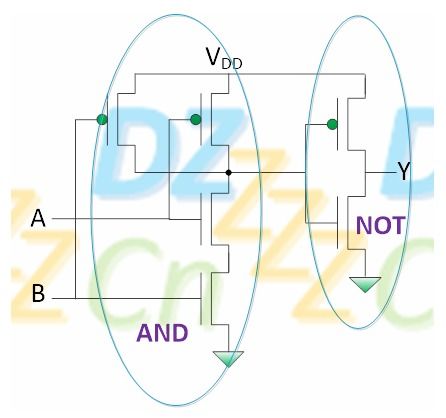

一、CMOS逻辑门的基本结构与工作原理

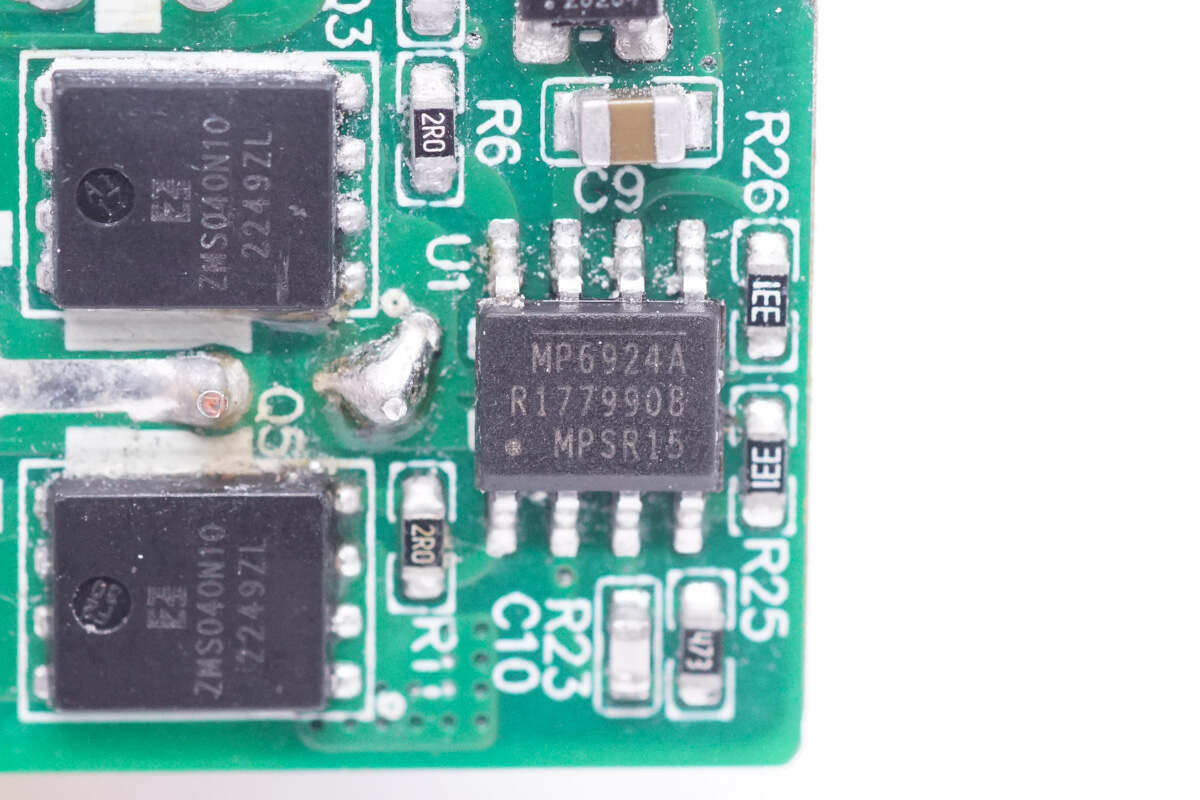

CMOS逻辑门的基本结构由两种类型的MOSFET(金属氧化物半导体场效应晶体管)构成:P沟道MOSFET(PMOS)和N沟道MOSFET(NMOS)。这两种晶体管以互补的方式连接。其核心工作原理在于:对于任何给定的输入组合,PMOS网络和NMOS网络中总有一个处于截止(关断)状态,从而在稳态下,从电源(VDD)到地(GND)之间没有直接的直流电流通路。这是CMOS电路静态功耗极低的根本原因。

以最基本的CMOS反相器(非门)为例:一个PMOS管连接在电源和输出端之间,一个NMOS管连接在输出端和地之间。当输入为高电平时,NMOS导通,PMOS截止,输出被下拉至低电平;当输入为低电平时,PMOS导通,NMOS截止,输出被上拉至高电平。这种推挽式输出结构提供了对负载电容的快速充放电能力。

二、复合逻辑门的设计:与非门(NAND)和或非门(NOR)

通过将多个PMOS和NMOS晶体管以特定方式组合,可以构建更复杂的逻辑功能。设计遵循以下规则:

- NMOS网络:实现逻辑函数的“下拉”路径,串联实现“与”操作,并联实现“或”操作。

- PMOS网络:实现逻辑函数的“上拉”路径,是NMOS网络的对偶,即串联对应“或”,并联对应“与”。

例如,一个二输入CMOS与非门由两个串联的NMOS管(下拉网络)和两个并联的PMOS管(上拉网络)构成。只有当两个输入均为高时,两个NMOS才都导通,将输出拉低;只要有一个输入为低,对应的PMOS就会导通,将输出拉高,完美实现了“与非”功能。

三、关键性能参数分析

在集成电路设计中,对逻辑门的分析远不止于逻辑功能,更关注其电气性能:

- 电压传输特性(VTC):描述了输出电压随输入电压变化的曲线。关键指标包括逻辑摆幅(通常接近VDD和GND)、噪声容限(高电平噪声容限和低电平噪声容限)以及开关阈值(VTC曲线中Vin=Vout的点)。

- 传播延迟:信号从输入变化到引起输出变化所需的时间,通常定义为输入输出波形50%点之间的时间差。它受晶体管尺寸、负载电容和电源电压的显著影响。

- 功耗:

- 动态功耗:主要由对负载电容充放电的开关功耗构成(∝ CL * VDD^2 * f),是CMOS电路功耗的主要来源。

- 静态功耗:在理想稳态下应接近于零,但实际上由于亚阈值漏电流等因素,深亚微米工艺下静态功耗已变得不可忽视。

- 扇入与扇出:扇入指门的输入数量,增加扇入会因晶体管串联而增加延迟。扇出指门能驱动的同类门输入数量,增加扇出会增加负载电容,同样导致延迟增加。

四、集成电路设计中的优化与折衷

在实际的CMOS集成电路设计中,逻辑门分析是性能、面积和功耗之间精细平衡的起点:

- 晶体管尺寸调整:通过调整PMOS和NMOS的沟道宽度(W),可以优化延迟、噪声容限和驱动能力。通常,为了使上升时间和下降时间对称,PMOS管的宽度被设计为NMOS管的2至3倍(因为空穴迁移率低于电子迁移率)。

- 工艺缩放的影响:随着工艺节点不断缩小,电源电压降低,器件物理特性发生变化(如短沟道效应加剧),这要求对逻辑门的模型和分析方法进行持续更新。互连线延迟相对于门延迟的比重增加,使得逻辑门驱动长线时的性能分析更为复杂。

- 功耗管理技术:基于对逻辑门功耗的深刻理解,设计者采用时钟门控、电源门控、多阈值电压技术等来有效控制动态和静态功耗。

五、先进逻辑门结构

为了满足高性能和低功耗的极端要求,标准CMOS逻辑门也在演进:

- 传输门逻辑:利用PMOS和NMOS并联构成双向开关,常用于构建多路选择器和锁存器。

- 动态逻辑:通过预充电和求值阶段,减少实现复杂逻辑所需的晶体管数量,从而获得更高的速度,但需要时钟控制且存在电荷泄漏等问题。

- 多米诺逻辑:是动态逻辑的一种改进,集成了静态反相器,提高了噪声容限和驱动能力。

结论

CMOS逻辑门电路分析是集成电路设计的核心基础。它不仅是理解数字电路如何工作的钥匙,更是进行高性能、低功耗、高可靠性芯片设计的根本。从简单的反相器到复杂的逻辑簇,对其静态特性、动态响应和功耗机理的精准建模与仿真,贯穿于从架构规划、逻辑综合到物理实现的整个IC设计流程。随着工艺进入纳米尺度乃至更小,对CMOS逻辑门行为的深入分析,包括其非理想效应和变异性的研究,将变得比以往任何时候都更加重要。

如若转载,请注明出处:http://www.laike-cloud.com/product/39.html

更新时间:2026-01-13 23:18:04