集成电路产业链 设计环节的核心技术与流程

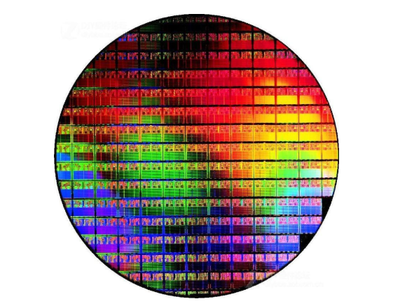

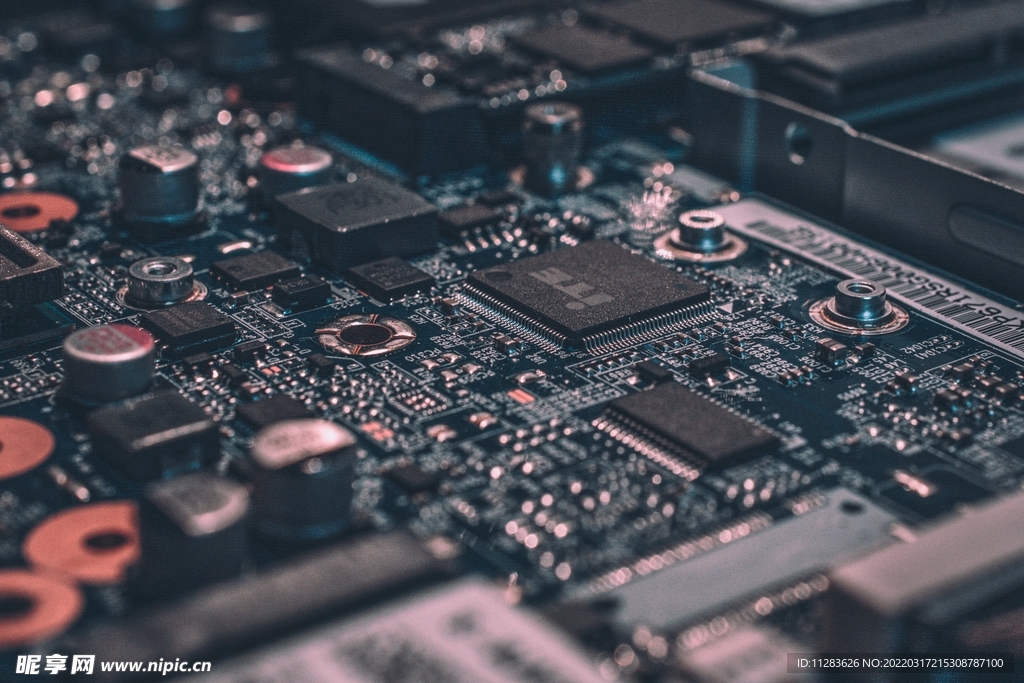

集成电路(Integrated Circuit,IC)是现代信息技术的基石,其产业链可分为设计、制造、封测三大核心环节,以及上游的材料、设备等支撑产业。其中,设计环节作为产业链的起点,承担着将创新理念转化为具体电路图与规格的关键任务,是技术附加值最高、智力最密集的部分。

一、设计环节的定义与重要性

集成电路设计,是指根据系统需求,利用电子设计自动化(EDA)工具,在芯片上规划、设计和验证数十亿个晶体管及其他元件的布局与连接关系,最终形成可供制造的光罩(掩膜版)图形数据(GDSII文件)。设计环节直接决定了芯片的功能、性能、功耗(PPA,即Performance、Power、Area)和成本,是整个产业链的“大脑”与“灵魂”。一个成功的芯片设计,往往需要深厚的系统知识、电路理论、工艺理解和算法功底。

二、主要设计流程与核心技术

典型的芯片设计是一个分层迭代的复杂过程,主要包含以下阶段:

- 系统架构与规格定义:基于应用场景(如智能手机、汽车、AI服务器),明确芯片的功能、性能指标、功耗预算、接口协议和成本目标。这是设计的“蓝图”阶段。

- 前端设计(逻辑设计):

- 寄存器传输级(RTL)设计:使用硬件描述语言(如Verilog、VHDL)将架构转化为可综合的寄存器级代码,描述数字电路的数据流与控制逻辑。

- 功能验证:通过仿真、形式验证等方法,确保RTL代码的功能与规格定义完全一致。验证工作量通常占设计总工作量的70%以上。

- 逻辑综合:利用EDA工具,将RTL代码映射到特定工艺库的标准单元(如与门、或门、触发器等),生成门级网表。此阶段会进行初步的时序和功耗分析。

- 后端设计(物理设计):

- 布图规划:确定芯片核心区域、模块摆放、电源网络和I/O引脚位置。

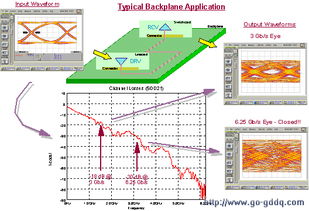

- 布局与布线:将门级网表中的单元精确放置在芯片上,并完成所有单元之间的金属连线。这是决定芯片面积、时序和功耗的关键步骤。

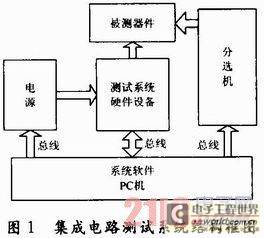

- 时序收敛与物理验证:通过静态时序分析(STA)确保所有信号路径满足时序要求;进行设计规则检查(DRC)和版图与原理图一致性检查(LVS),确保版图符合制造工艺规则且与网表一致。

- 签核:完成最终的时序、功耗、信号完整性、可靠性等分析,生成最终的GDSII版图文件交付给晶圆厂。

三、设计环节的关键参与者与商业模式

- 设计公司类型:

- 无晶圆厂设计公司:专注于设计,将制造、封测外包给专业代工厂(如台积电、中芯国际)和封测厂。代表企业有高通、英伟达、AMD、华为海思等。

- 集成器件制造商:拥有设计与制造能力,如英特尔、三星。

- 设计服务与IP供应商:提供设计服务、验证服务或出售预先设计好的、可复用的功能模块(IP核,如ARM的CPU核、Synopsys的接口IP)。

- 核心支撑:EDA工具与IP核:

- EDA工具:是设计的“画笔”与“脚手架”,覆盖从设计到验证的全流程。全球市场主要由新思科技(Synopsys)、楷登电子(Cadence)和西门子EDA(原Mentor Graphics)三大巨头垄断。

- IP核:极大地提高了设计效率和可靠性,是现代SoC(片上系统)设计的基石。

四、面临的挑战与发展趋势

- 挑战:随着工艺节点进入纳米尺度(如3nm、2nm),设计面临物理效应复杂(如量子隧穿)、功耗墙、设计成本指数级上升(先进节点芯片设计成本可达数亿美元)、人才短缺等严峻挑战。

- 趋势:

- 异构集成与Chiplet:通过将不同工艺、功能的芯粒(Chiplet)进行先进封装集成,以平衡性能、成本与开发周期。

- AI赋能设计:利用人工智能/机器学习优化布局布线、加速验证和设计空间探索。

- 系统级协同优化:从传统的芯片设计转向芯片-封装-板级-系统的全栈协同设计与优化。

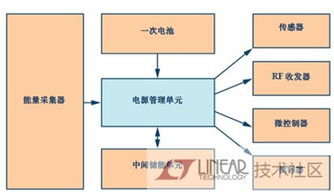

- 新兴领域驱动:高性能计算、人工智能、汽车电子、物联网等对芯片的定制化、高能效需求,催生了更多专用芯片(ASIC)和领域专用架构(DSA)。

###

集成电路设计环节是连接市场需求与物理实现的桥梁,是知识、工具和创造力高度融合的领域。它不仅推动着摩尔定律的延续,更在“后摩尔时代”通过架构与系统创新,持续引领信息产业的变革。对于我国而言,突破EDA工具、高端IP核等关键环节的技术壁垒,构建安全可控的设计生态,是提升集成电路产业核心竞争力的重中之重。

如若转载,请注明出处:http://www.laike-cloud.com/product/64.html

更新时间:2026-04-14 04:03:03